# Personal Communications

# IC Handbook

# DATASHEET ANNOTATION

GPS annotate datasheets in the top right hand corner of the first page, to indicate product status. These annotations are as follows:-

#### TARGET SPECIFICATION

This is the most tentative form of information and represents a very preliminary product specification. No actual design work on the product has started.

# PRELIMINARY INFORMATION

The product is in design and development. The datasheet represents the product as it is understood but details may change.

#### ADVANCE INFORMATION

The product design is complete and final characterisation for volume production is well in hand.

## No annotation

The product parameters are fixed and the product is available to datasheet specification in volume.

If you have any queries about the status of any GPS product, please contact your nearest GPS Customer Service Centre.

# PERSONAL COMMUNICATIONS

IC Handbook

# Foreword

This latest Personal Communications IC Handbook from GEC Plessey Semiconductors introduces numerous new devices for this rapidly expanding market. GEC Plessey Semiconductors has been involved in many successful wireless communications projects, providing a vital link between high performance and cost effective implementations in applications as diverse as credit card pagers and digital cordless telephones.

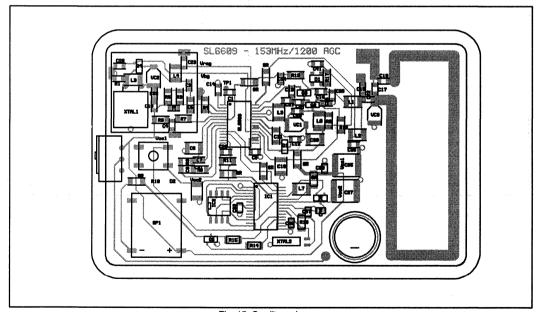

These applications share a number of common goals, small size and low power are paramount, and these are also the goals of our IC design teams. New products such as the SP8715 family of prescalers offer low voltage and low current consumption using state of the art sub micron bipolar processes, whilst the SL6609 direct conversion paging receiver offers improved sensitivity and reduced board area over its predecessor. CMOS developments include higher functionality synthesisers with features such as Fractional N interpolation for improved locking speed and a POCSAG paging decoder to compliment the SL6609.

High performance extends to packaging and all the components in this handbook are offered in industry standard surface mount packages, with latest developments using fine lead pitches of 0.65 and 0.5mm.

Finally, the Quality Assurance programmes that are applied to GEC Plessey Semiconductors products (from consumer electronics to defense projects) are applied to all Personal Communications products with rigour. Performance and long term reliability are therefore guaranteed in what can be a demanding operating environment.

# Contents

|              |                             | PAGE |

|--------------|-----------------------------|------|

| *            |                             |      |

| Product List | - By Circuit Type           | 4    |

|              | - Alpha numeric             | 6    |

| Section 1:   | PLLs (Phased Lock Loop)     | 7    |

| Section 2:   | IF Products                 | 77   |

| Section 3:   | Prescalers                  | 107  |

| Section 4:   | RF Front Ends               | 147  |

| Section 5:   | Amplifiers                  | 173  |

| Section 6:   | CODEC                       | 195  |

| Section 7:   | Paging Receivers & Decoders | 213  |

| Section 8:   | Application Notes           | 261  |

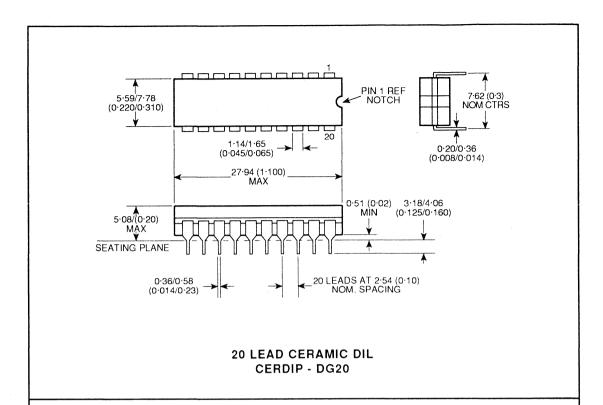

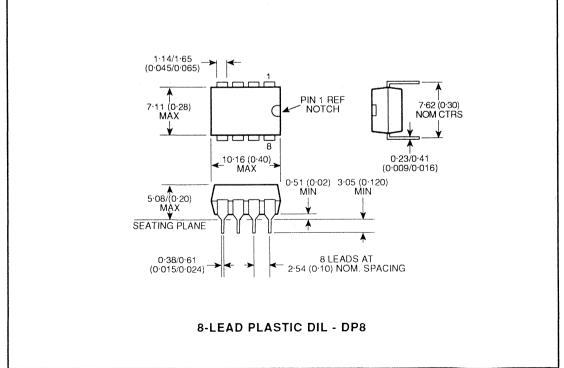

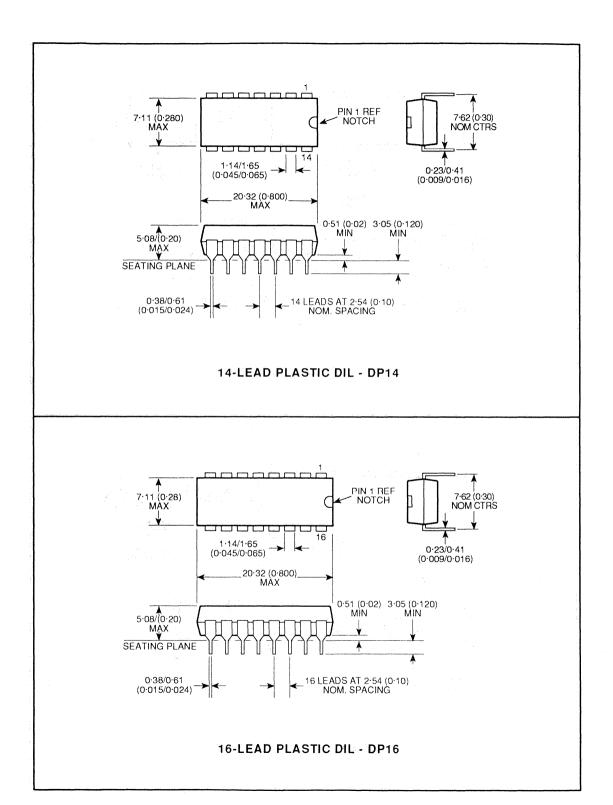

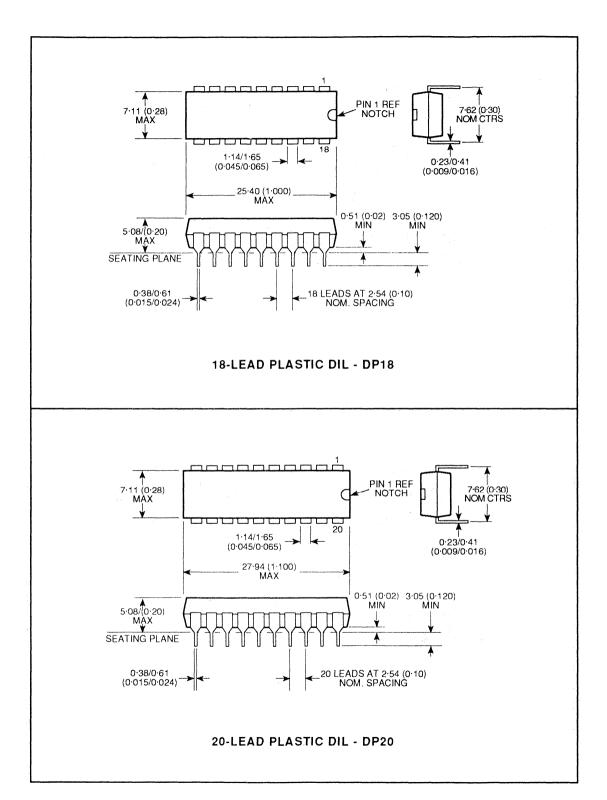

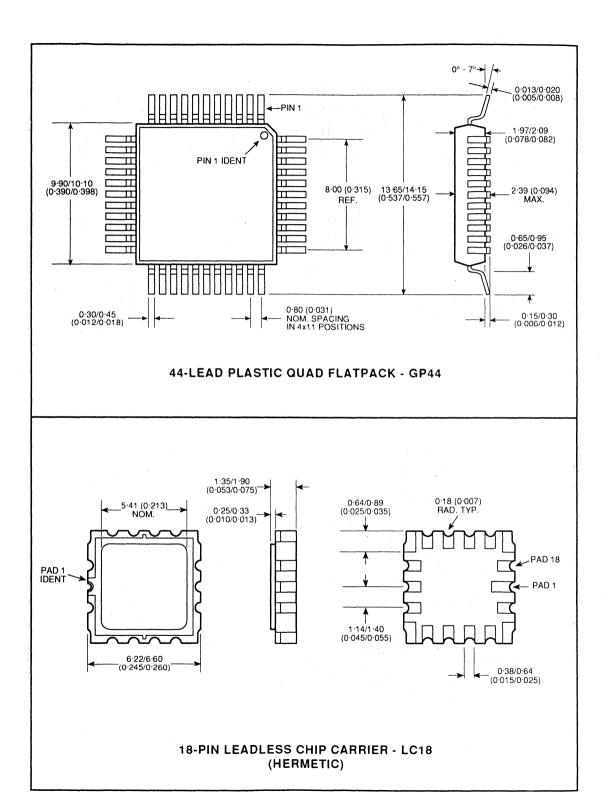

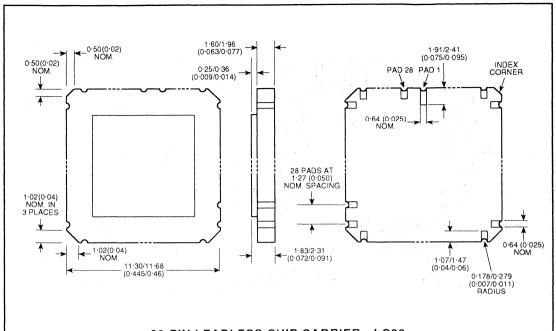

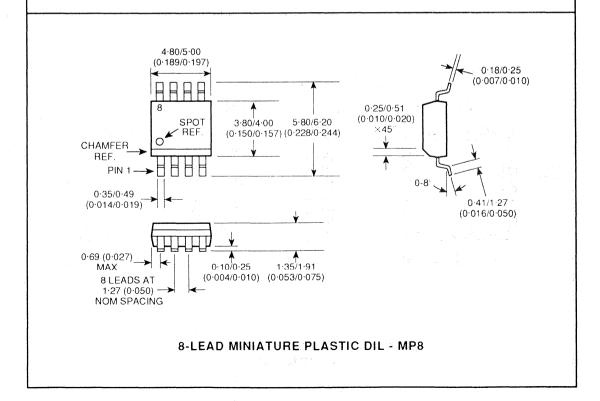

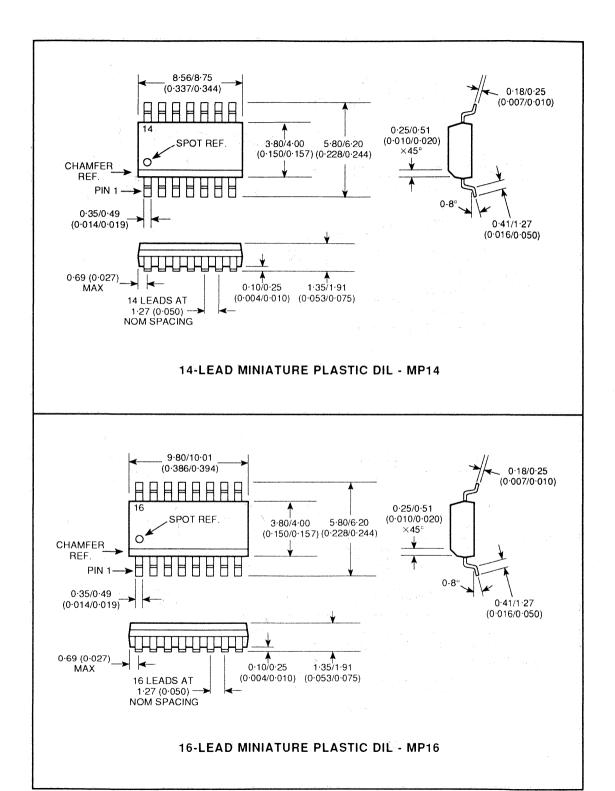

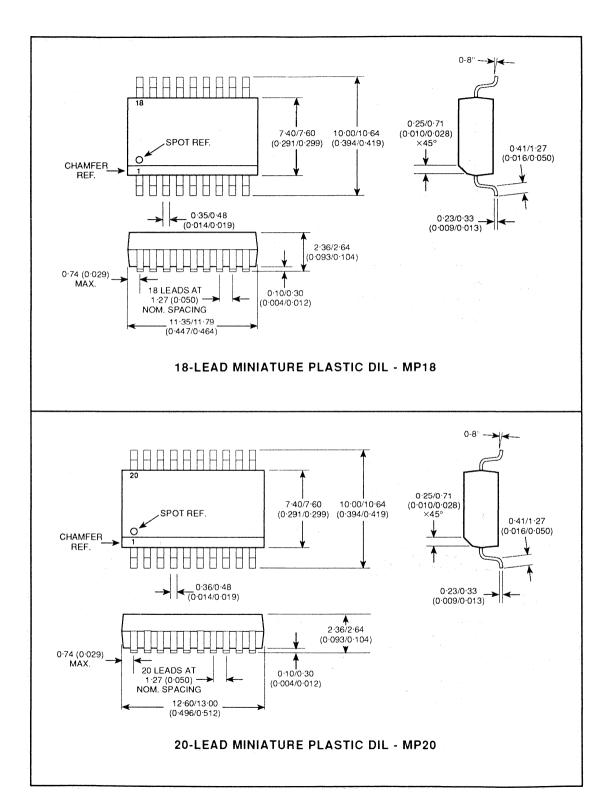

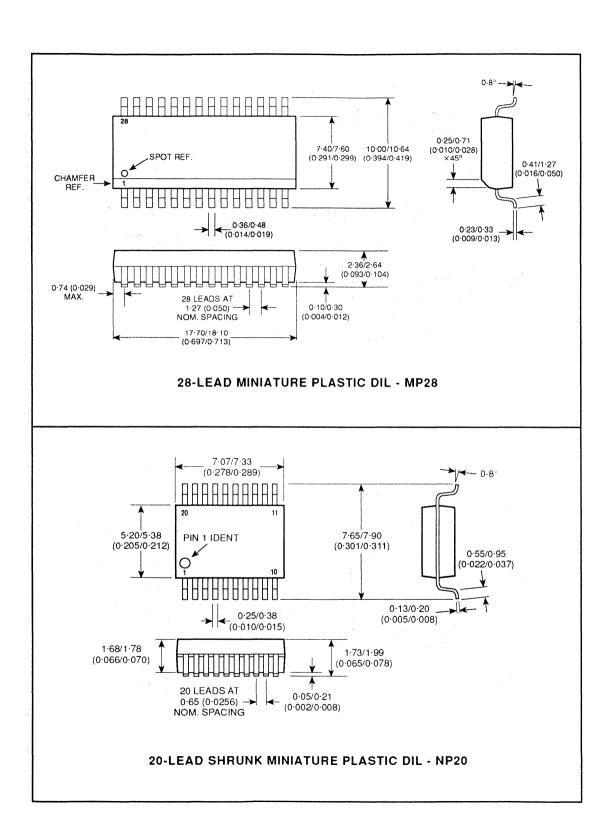

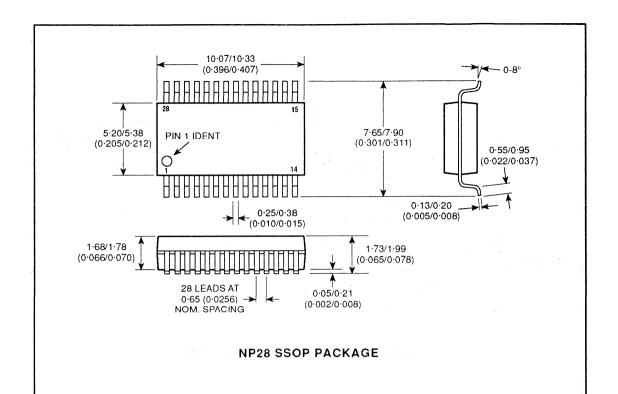

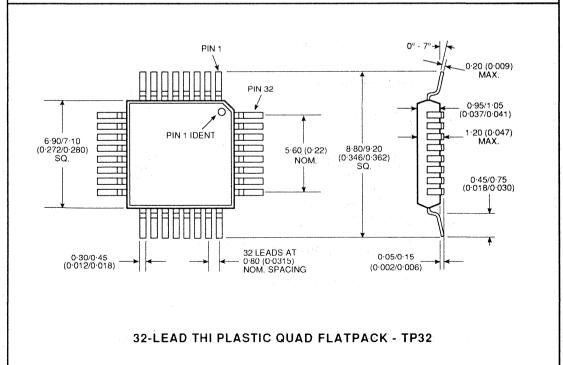

| Section 9:   | Package Outlines            | 347  |

| Section 10:  | GPS Locations               | 359  |

# Product List - by circuit type PLLs (Phased Lock Loop)

| Type No.  | Description                                                                          | Page |

|-----------|--------------------------------------------------------------------------------------|------|

| NJ8820    | Frequency synthesiser (PROM interface)                                               | 9    |

| NJ8821    | Frequency synthesiser (microprocessor interface) with resettable counters            | 14   |

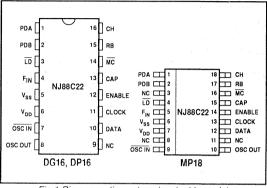

| NJ88C22** | Frequency synthesiser (microprocessor serial interface)                              | 18   |

| NJ8823**  | Frequency synthesiser (microprocessor interface) with non-resettable counters        | 23   |

| NJ88C24** | Frequency synthesiser (microprocessor serial interface)                              | 27   |

| NJ88C25** | Frequency synthesiser (microprocessor serial interface)                              | 32   |

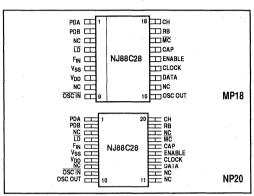

| NJ88C28   | Frequency synthesiser (microprocessor serial interface) with non-resettable counters | 37   |

| NJ88C29   | Frequency synthesiser (microprocessor serial interface) with non-resettable counters | 43   |

| NJ88C30** | VHF synthesiser                                                                      | 49   |

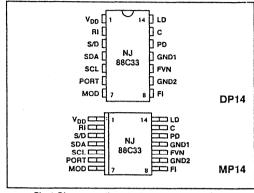

| NJ88C33   | Frequency synthesiser (I2C bus programmable) with current source outputs             | 54   |

| NJ88C50   | Dual low power frequency synthesiser                                                 | 64   |

# **IF Products**

| Type No.  | Description                                          | Page |

|-----------|------------------------------------------------------|------|

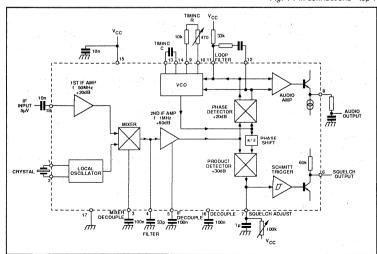

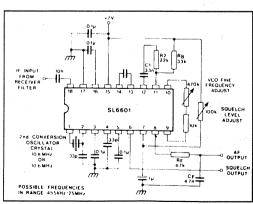

| SL6601C** | FM IF, PLL detector (double conversion) and RF mixer | 79   |

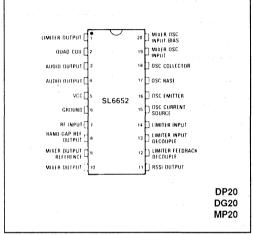

| SL6652**  | Low power IF/AF circuit for FM cellular radio        | 85   |

| SL6654**  | Low power IF/AF circuit for FM cellular radio        | 92   |

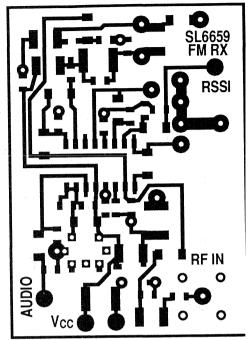

| SL6659    | Low power IF/AF circuit (with RSSI) for FM radio     | 98   |

# Prescalers

| Type No.   | Description                                        | Page |

|------------|----------------------------------------------------|------|

| SP8704**   | 950MHz very low current divide by 128/129 or 64/64 | 109  |

| SP8713     | 1100MHz very low current three modulus divider     | 111  |

| SP8714     | 2100MHz vey low current multi-modulus divider      | 118  |

| SP8715     | 1100MHz very low current multi-modulus divider     |      |

| SP8716/8/9 | 520MHz divide by 40/41 + 64/64 + 80/81             | 132  |

| SP8789     | 225MHz divide by 20/21 two modulus divider         |      |

| SP8792/3   | 520MHz divide by 80/81 + 40/41                     |      |

| SP8795     | 225MHz divide by 32/33                             | 141  |

| SP8799     | 225MHz divide by 10/11                             | 144  |

# **RF Front Ends**

| Type No. | Description          | Page |

|----------|----------------------|------|

| SL6442   | 1GHz amplifier/mixer | 149  |

| SL6444   | 1GHz amplifier/mixer | 159  |

| Amplifiers |                               |      |

|------------|-------------------------------|------|

| Type No.   | Description                   | Page |

| SL562      | Low noise programmable op-amp | 175  |

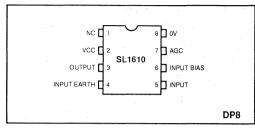

| SL1610     | RF/IF.Amplifier               | 178  |

| SL6140     | 400MHz wideband AGC amplifier | 181  |

| SL6270C    | Gain controlled pre-amplifier | 189  |

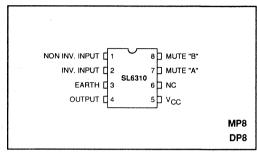

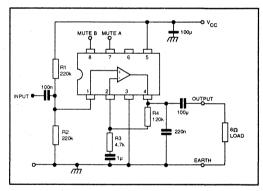

| SL6310C    | Switchable audio amplifier    | 192  |

# CODEC

| Type No. | Description                                                  | Page |

|----------|--------------------------------------------------------------|------|

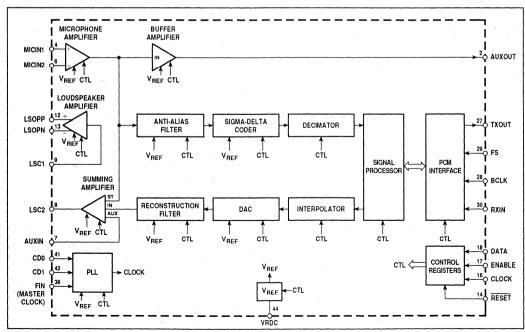

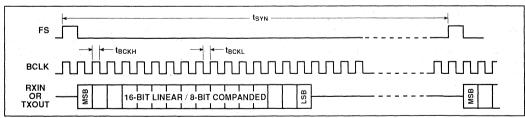

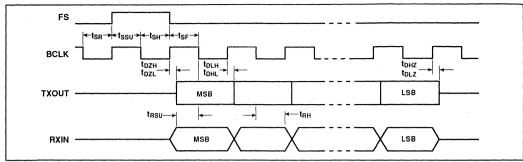

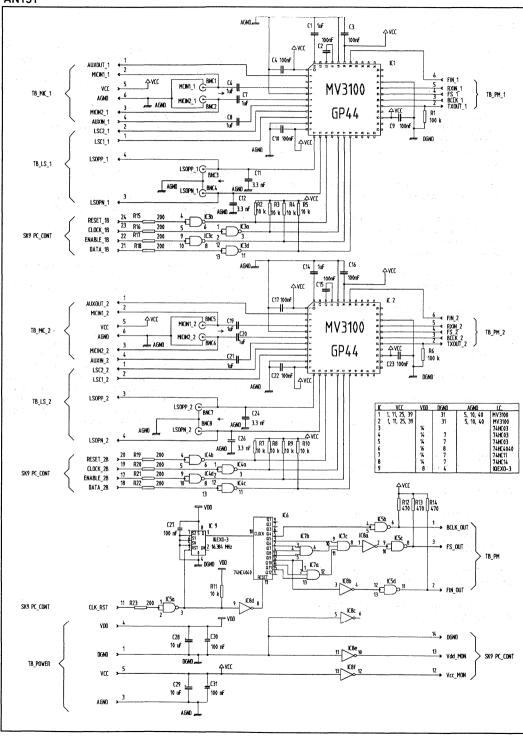

| MV3100   | 3V CODEC with analog interface for digital mobile telephones | 197  |

# Paging Receivers & Decoders

| Type No. | Description                                |     | Page |

|----------|--------------------------------------------|-----|------|

| MV6639   | POCSAG decoder                             |     | 215  |

| MV6640*  | POCSAG decoder                             |     | 234  |

| SL6609   | Direct conversion FSK data receiver        | 100 | 235  |

| SL6619*  | 450MHz direct conversion receiver with AFC |     | 248  |

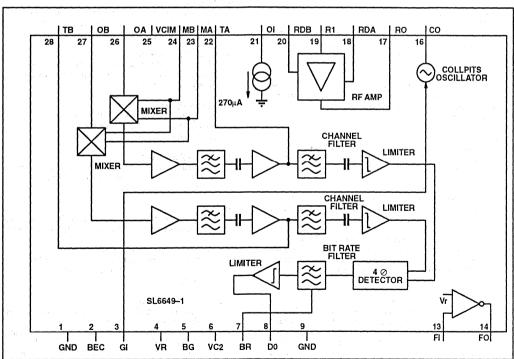

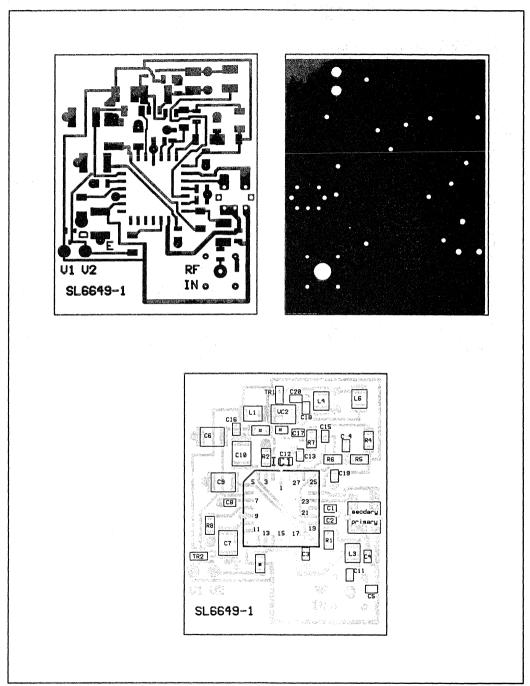

| SL6649-1 | 200MHz direct conversion FSK data receiver |     | 249  |

Outline or development details only - contact GPS Customer Services (see page 359)

For maintenance purposes only

# Product List - alpha numeric

| Type No.  | Description                                                                             | Page |

|-----------|-----------------------------------------------------------------------------------------|------|

| MV3100    | 3V CODEC with analog interface for digital mobile telephones                            | 197  |

| MV6639    | POCSAG decoder                                                                          | 215  |

| MV6640*   | POCSAG decoder                                                                          | 234  |

| NJ8820    | Frequency synthesiser (PROM interface)                                                  | 9    |

| NJ8821    | Frequency synthesiser (microprocessor interface) with resettable counters               | 14   |

| NJ88C22** | Frequency synthesiser (microprocessor serial interface)                                 | 18   |

| NJ8823**  | Frequency synthesiser (microprocessor interface) with non-resettable counters           | 23   |

| NJ88C24** | Frequency synthesiser (microprocessor serial interface)                                 | 27   |

| NJ88C25** | Frequency synthesiser (microprocessor serial interface)                                 | 32   |

| NJ88C28   | Frequency synthesiser (microprocessor serial interface) with non-resettable counters    | 37   |

| NJ88C29   | Frequency synthesiser (microprocessor serial interface) with non-resettable counters    | 43   |

| NJ88C30** | VHF synthesiser                                                                         | 49   |

| NJ88C33   | Frequency synthesiser (I2C bus programmable) with current source phase detector outputs | 54   |

| NJ88C50   | Dual low power frequency synthesiser                                                    | 64   |

| SL562     | Low noise programmable op-amp                                                           | 175  |

| SL1610    | RF/IF Amplifier                                                                         | 178  |

| SL6140    | 400MHz wideband AGC amplifier                                                           | 181  |

| SL6270C   | Gain controlled pre-amplifier                                                           | 189  |

| SL6310C   | Switchable audio amplifier                                                              | 192  |

| SL6442    | 1GHz amplifier/mixer                                                                    | 149  |

| SL6444    | 1GHz amplifier/mixer                                                                    | 159  |

| SL6601C** | FM IF, PLL detector (double conversion) and RF mixer                                    | 79   |

| SL6609    | Direct conversion FSK data receiver                                                     | 235  |

| SL6619*   | 450MHz direct conversion receiver with AFC                                              | 248  |

| SL6649-1  | 200MHz direct conversion FSK data receiver                                              | 249  |

| SL6652**  | Low power IF/AF circuit for FM cellular radio                                           | 85   |

| SL6654**  | Low power IF/AF circuit for FM cellular radio                                           | 92   |

| SL6659    | Low power IF/AF circuit (with RSSI) for FM radio                                        | 98   |

| SP8704**  | 950MHz very low current divide by 128/129 or 64/64                                      | 109  |

| SP8713    | 1100MHz very low current three modulus divider                                          | 111  |

| SP8714    | 2100MHz very low current multi-modulus divider                                          | 118  |

| SP8715    | 1100MHz very low current multi-modulus divider                                          | 125  |

| SP8716    | 520MHz divide by 40/41                                                                  | 132  |

| SP8718    | 520MHz divide by 64/64                                                                  | 132  |

| SP8719    | 520MHz divide by 80/81                                                                  | 132  |

| SP8789    | 225MHz divide by 20/21                                                                  | 135  |

| SP8792    | 225MHz divide by 80/81                                                                  | 138  |

| SP8793    | 225MHz divide by 40/41                                                                  | 138  |

| SP8795    | 225MHz divide by 32/33                                                                  | 141  |

| SP8799    | 225MHz divide by 10/11                                                                  | 144  |

<sup>\*</sup> Outline or development details only - contact GPS Customer Services (see page 359)

<sup>\*\*</sup> For maintenance purposes only

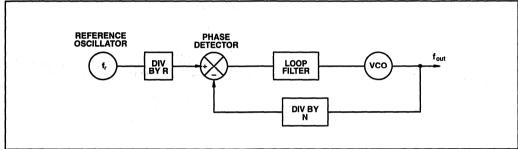

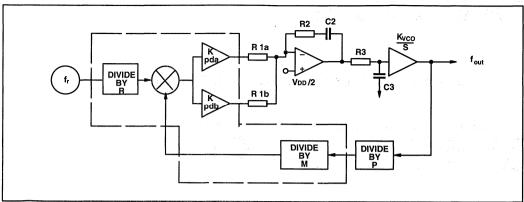

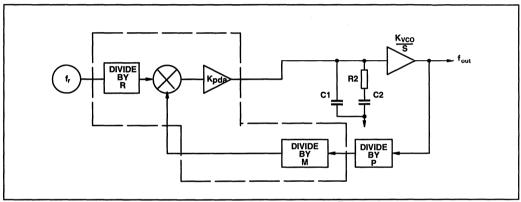

# Section 1 PLLs (Phased Lock Loop)

# **NJ8820**

# FREQUENCY SYNTHESISER (PROM INTERFACE)

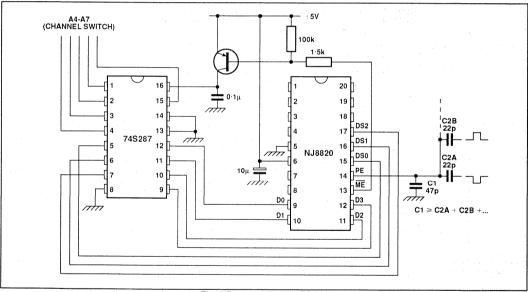

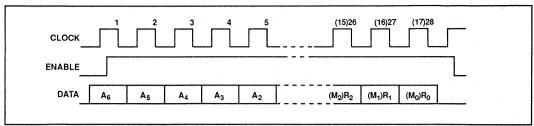

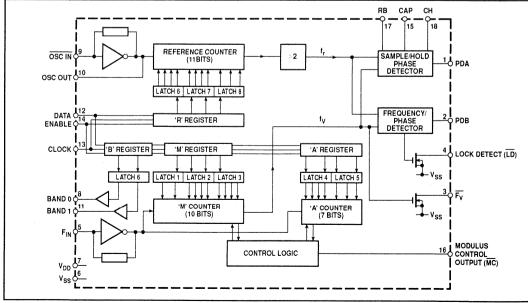

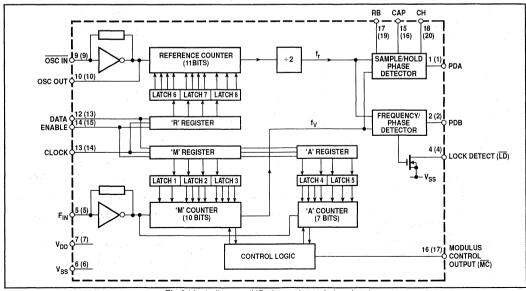

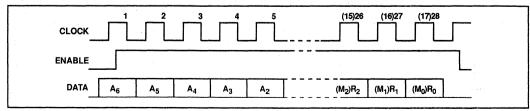

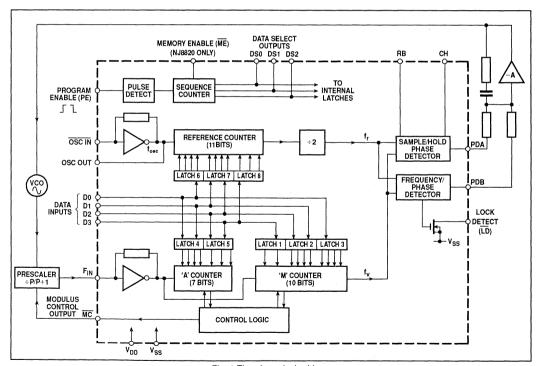

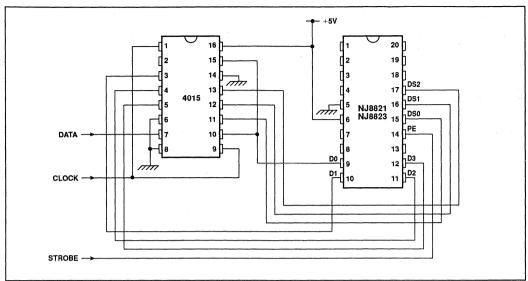

The NJ8820 is a synthesiser circuit fabricated on the GPS CMOS process and is capable of achieving high sideband attenuation and low noise performance. It contains a reference oscillator, 11-bit programmable reference divider, digital and sample-and-hold comparators, 10-bit programmable 'M' counter, 7-bit programmable 'A' counter and the necessary control and latch circuitry for accepting and latching the input data.

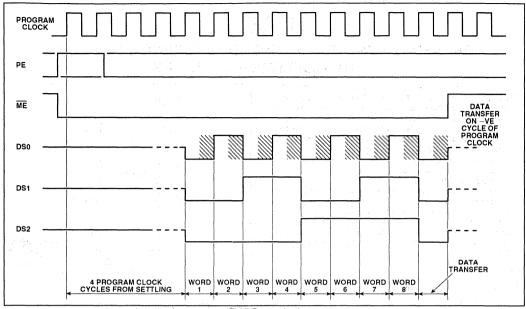

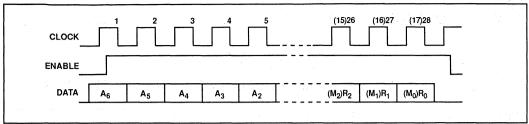

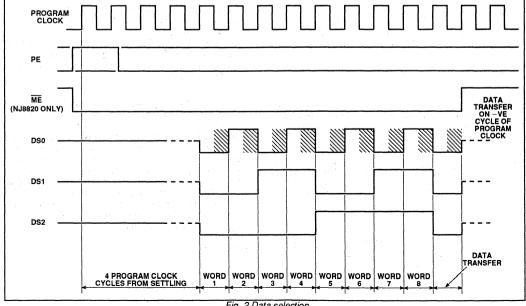

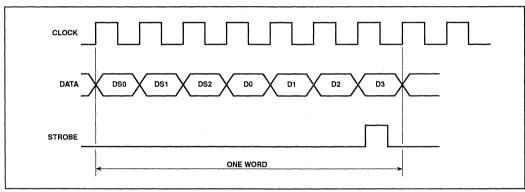

Data is presented as eight 4-bit words read from an external memory, with the necessary timing signals generated internally.

It is intended to be used in conjunction with a two-modulus prescaler such as the SP8710 series to produce a universal binary coded synthesiser.

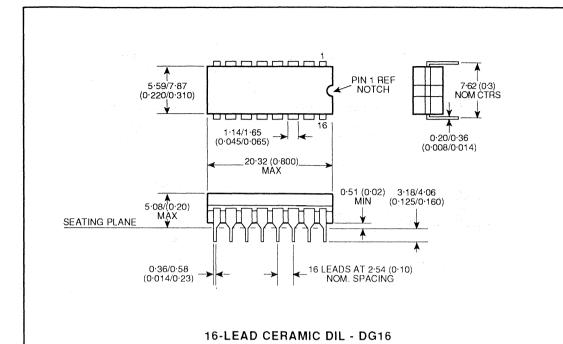

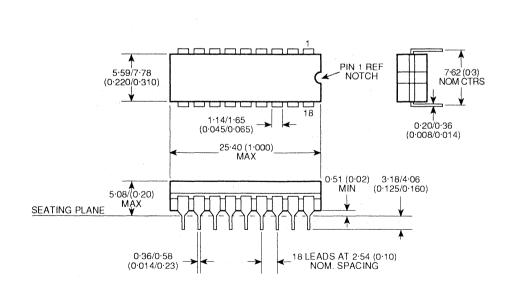

The NJ8820 is available in Plastic DIL (DP) and Miniature Plastic DIL (MP) packages, both with operating temperature range of -30°C to +70°C. The NJ8820MA is available only in Ceramic DIL package with operating temperature range of -40°C to +85°C.

# **FEATURES**

- Low Power Consumption

- Direct Interface to ROM or PROM

- High Performance Sample and Hold Phase Detector

- >10MHz Input Frequency

# ORDERING INFORMATION

NJ8820 BA DP Plastic DIL Package

NJ8820 BA MP Miniature Plastic DIL Package

NJ8820 MA DG Ceramic DIL Package

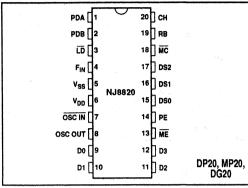

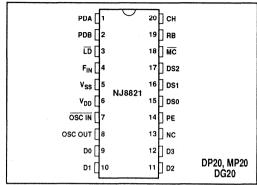

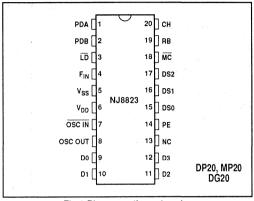

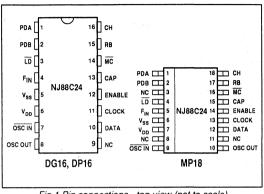

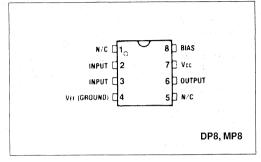

Fig.1 Pin connections - top view

# **ABSOLUTE MAXIMUM RATINGS**

Supply voltage, V<sub>DD</sub> – V<sub>SS</sub> –0.5V to 7V Input voltage

Open drain outputs, pins 3 and 13

7V

All other pins  $V_{SS}$  = 0.3V to  $V_{DD}$  + 0.3V Storage temperature  $-65^{\circ}$ C to +150°C (DG package, NJ8820MA)

Storage temperature -55°C to +125°C (DP and MP packages, NJ8820)

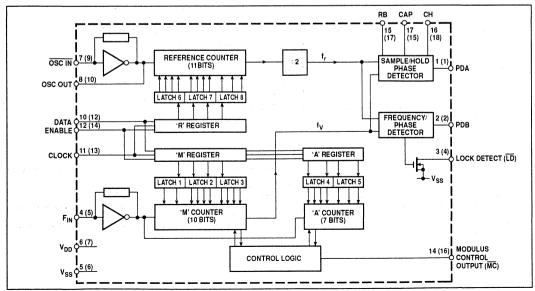

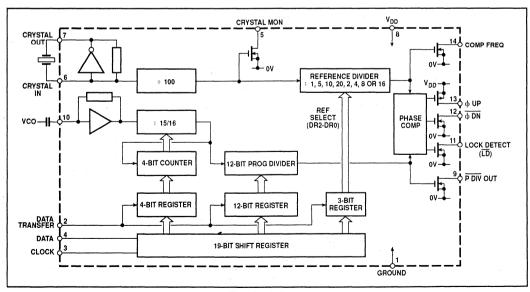

DATA SELECT MEMORY ENABLE OUTPUTS RB CH (ME) DS0 DS1 DS2 16 17 13 20 PULSE SEQUENCE INTERNAL PROGRAM DETECT ENABLE (PE)  $\Gamma$ REFERENCE COUNTER SAMPLE/HOLD OSC IN (11BITS) PHASE OSC OUT LATCH 6 LATCH 7 LATCH 8 FREQUENCY/ PHASE PDB D0 DATA D1 D2 LOCK DETECT (LD) LATCH 1 LATCH 2 LATCH 3 LATCH 4 LATCH 5 'M' COUNTER 'A' COUNTER (10 BITS) (7 BITS) MODULUS CONTROL LOGIC CONTROL OUTPUT (MC)

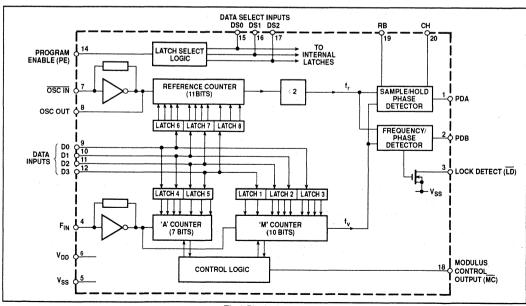

Fig.2 Block diagram

# NJ8820

# ELECTRICAL CHARACTERISTICS AT VDD = 5V

Test conditions unless otherwise stated:

V<sub>DD</sub>-V<sub>SS</sub>=5V ±0·5V. Temperature range NJ8820 BA: -30°C to +70°C; NJ8820 MA: -40°C to +85°C DC Characteristics

| Characteristic                |                   | Value |       | Units |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------------------------|-------------------|-------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                               |                   | Тур.  | Max.  | Units | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

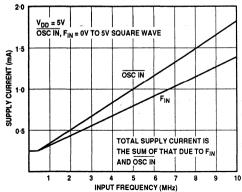

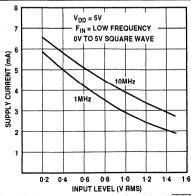

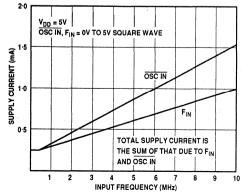

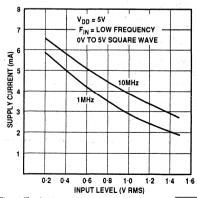

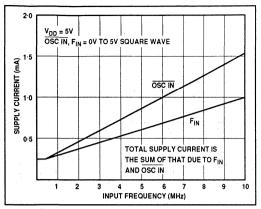

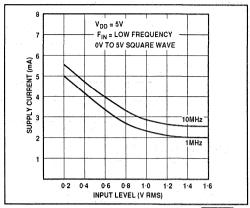

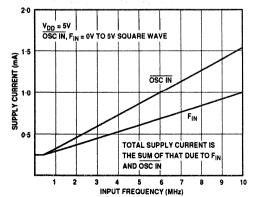

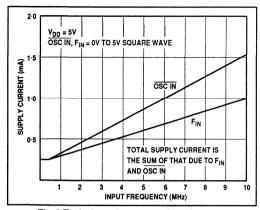

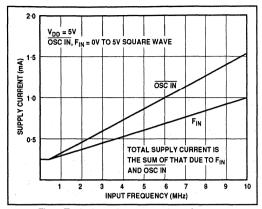

| Supply current                |                   | 3.5   | 5.5   | mA    | f <sub>osc</sub> , f <sub>FIN</sub> = 10MHz ) 0 to 5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                               |                   | 0.7   | 1.5   | mA    | f <sub>osc</sub> , f <sub>FIN</sub> = 1.0MHz square wave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| OUTPUT LEVELS                 | Î                 |       | 112   | 1915  | wave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Memory Enable Output (ME)     |                   |       |       | 1,441 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Low level                     | 1                 |       | 0.4   | V     | I <sub>SINK</sub> = 4mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Open drain pull-up voltage    | 1                 |       | 7     | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Data Select Outputs (DS0-DS2) |                   |       |       |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| High level                    | 4.6               |       | 4     | V     | I <sub>SOURCE</sub> = 1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Low level                     |                   |       | 0.4   | V     | I <sub>SINK</sub> = 2mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Modulus Control Output (MC)   |                   |       | 49.00 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| High level                    | 4.6               |       |       | V     | I <sub>SOURCE</sub> = 1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Low level                     | 1                 |       | 0.4   | V     | I <sub>SINK</sub> = 1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Lock Detect Output (LD)       |                   |       |       |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Low level                     |                   |       | 0.4   | V     | I <sub>SINK</sub> = 4mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Open drain pull-up voltage    |                   |       | 7     | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PDB Output                    |                   |       |       |       | A Programme A Prog |  |

| High level                    | 4.6               |       |       | V     | I <sub>SOURCE</sub> = 5mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Low level                     | 1.0               | 100   | 0.4   | V     | I <sub>SINK</sub> = 5mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 3-state leakage current       |                   |       | ±0·1  | μА    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                               |                   |       |       | '     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| INPUT LEVELS                  |                   |       |       |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Data Inputs (D0-D3)           |                   |       |       |       | granger in the second of the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| High level                    | 4.25              |       |       | V 1   | TTL compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Low level                     |                   |       | 0.75  | V     | See note 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Program Enable Input (PE)     |                   |       |       |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Trigger level                 | V <sub>BIAS</sub> |       |       | V     | V <sub>BIAS</sub> = self-bias point of PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                               | ±100mV            |       |       | .50   | (nominally V <sub>DD</sub> /2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

# **AC Characteristics**

| Characteristic                                                  |      | Value          |           |       | <u> </u>                                              |  |

|-----------------------------------------------------------------|------|----------------|-----------|-------|-------------------------------------------------------|--|

|                                                                 |      | Min. Typ. Max. |           | Units | Conditions                                            |  |

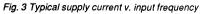

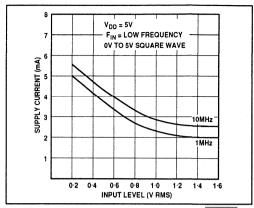

| F <sub>IN</sub> and OSC IN input level                          | 200  |                | i era i i | mVRMS | 10MHz AC-coupled sinewave                             |  |

| Max. operating frequency, f <sub>FIN</sub> and f <sub>osc</sub> | 10.6 |                |           | MHz   | Input squarewave V <sub>DD</sub> to V <sub>SS</sub> , |  |

|                                                                 |      | 100            |           |       | See note 5.                                           |  |

| Propagation delay, clock to MC                                  |      | 30             | 50        | ns    | See note 2.                                           |  |

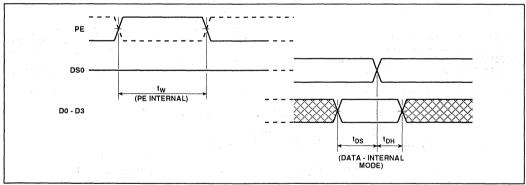

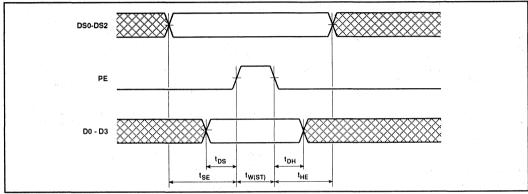

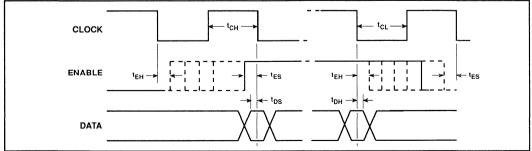

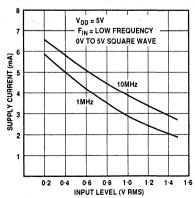

| PE pulse length, t <sub>W</sub>                                 | 5    |                |           | μs    | Pulse to V <sub>SS</sub> or V <sub>DD</sub> .         |  |

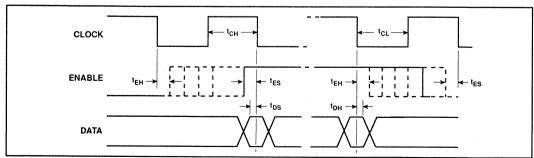

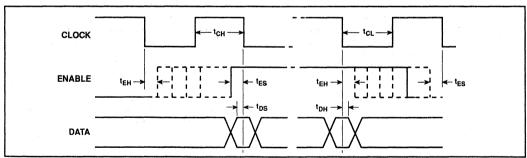

| Data set-up time, t <sub>DS</sub>                               | 1    |                |           | μs    | , and a second                                        |  |

| Data hold time, t <sub>DH</sub>                                 | 10   |                |           | ns    |                                                       |  |

| Digital phase detector propagation delay                        |      | 500            | 1         | ns    |                                                       |  |

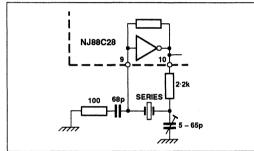

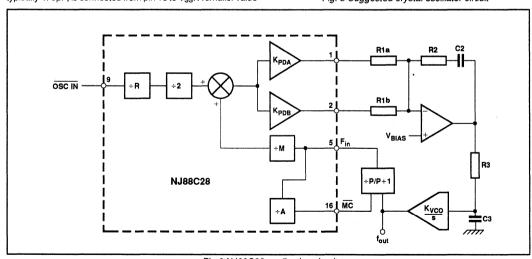

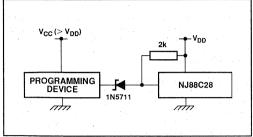

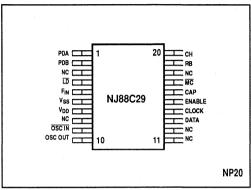

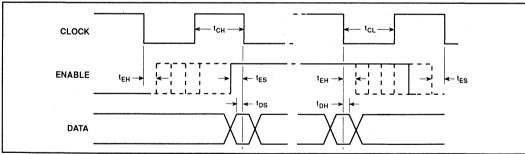

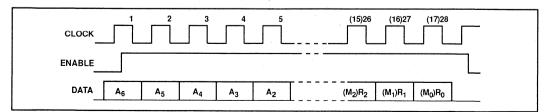

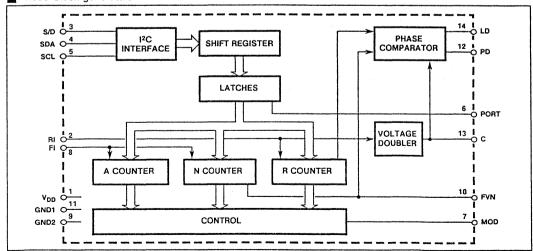

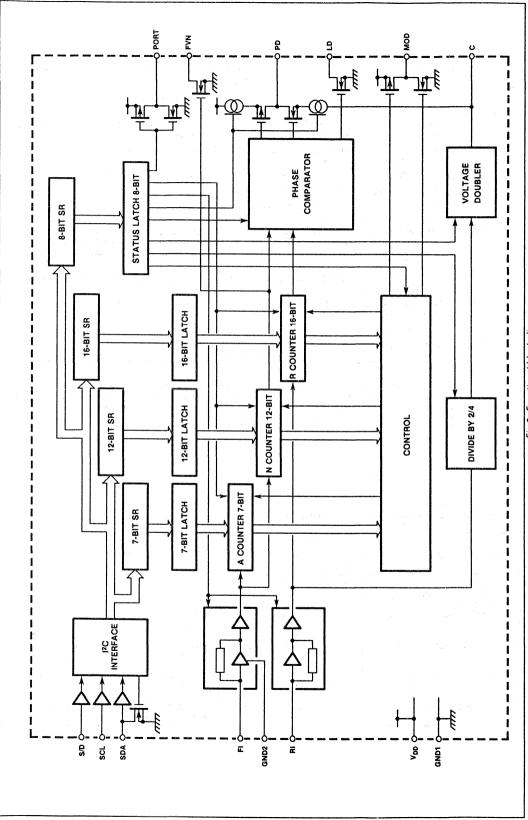

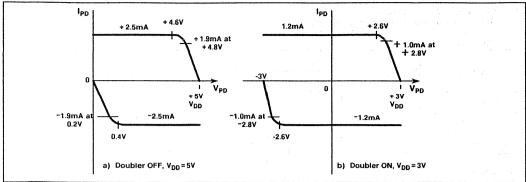

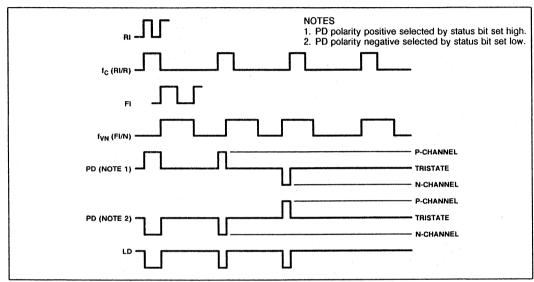

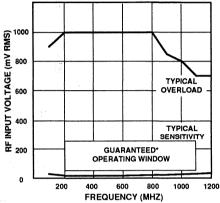

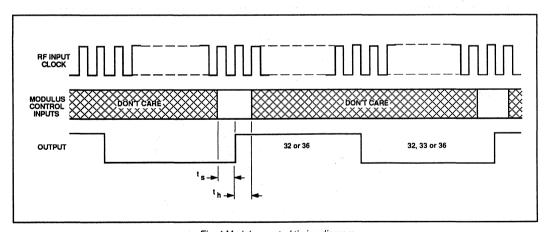

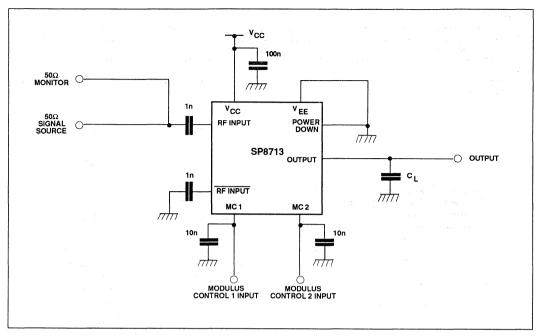

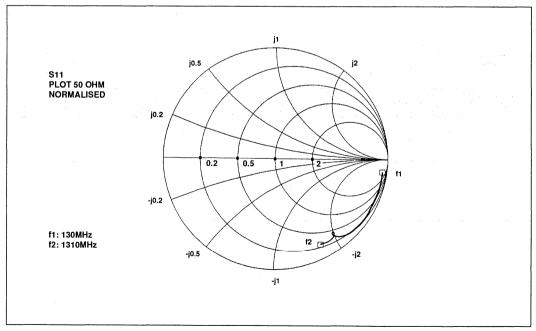

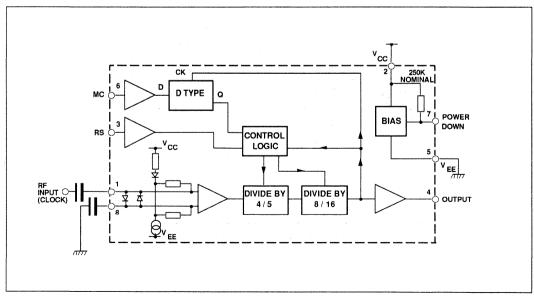

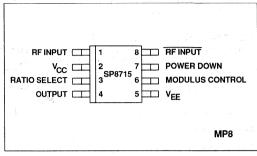

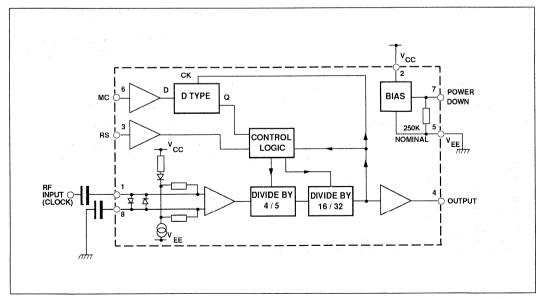

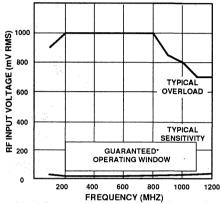

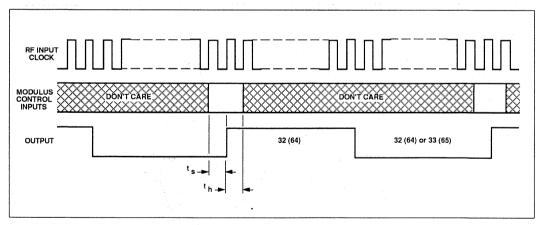

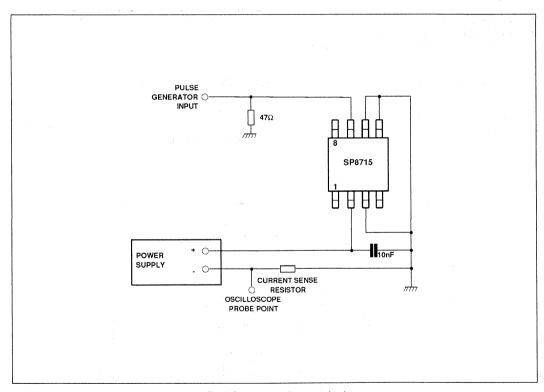

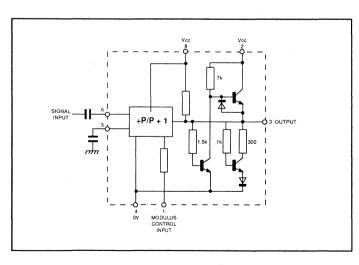

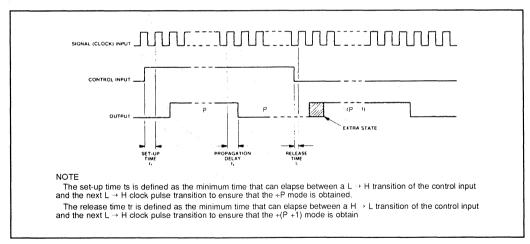

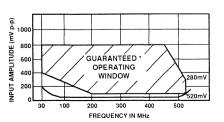

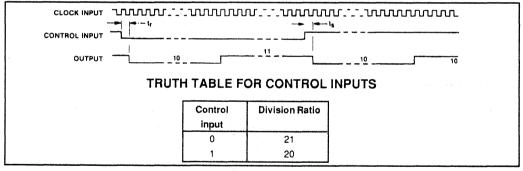

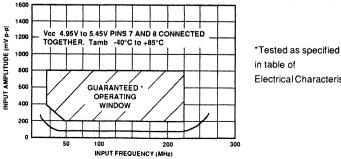

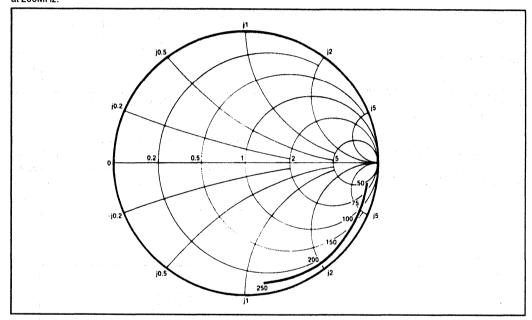

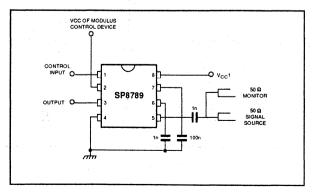

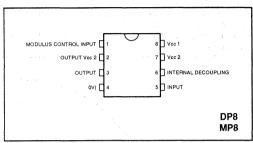

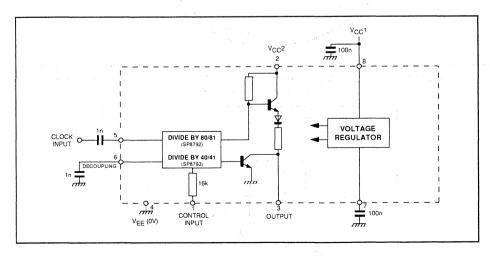

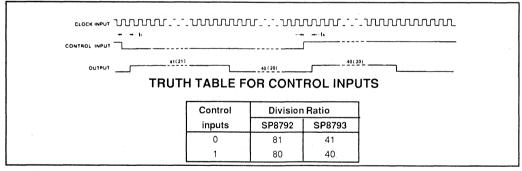

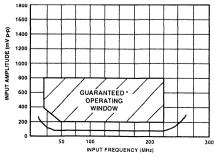

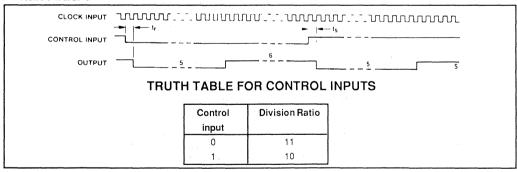

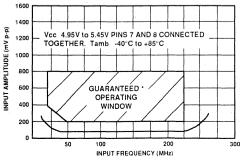

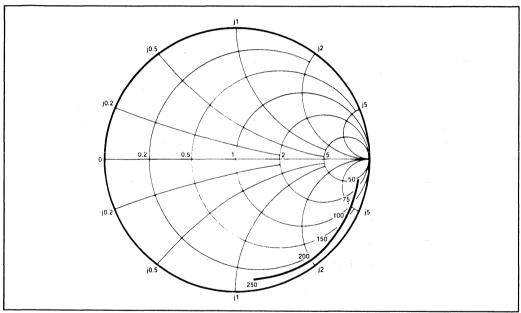

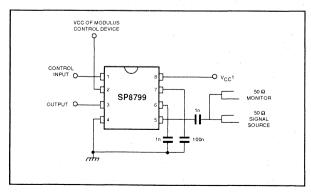

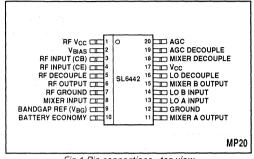

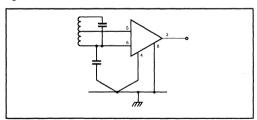

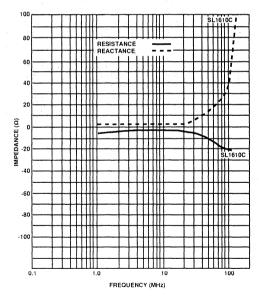

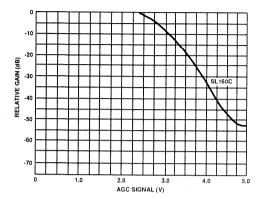

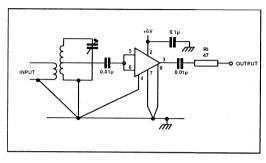

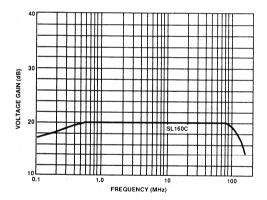

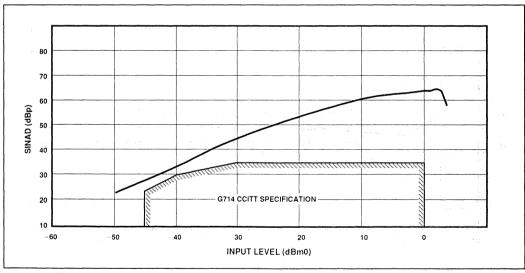

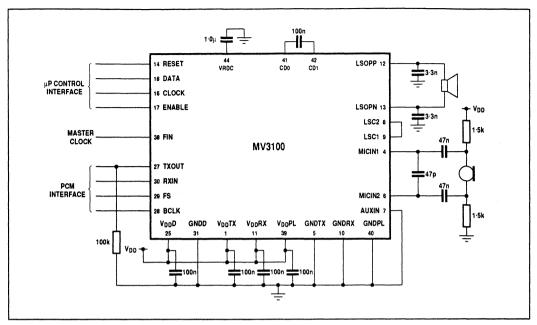

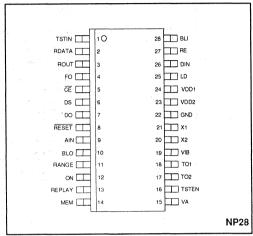

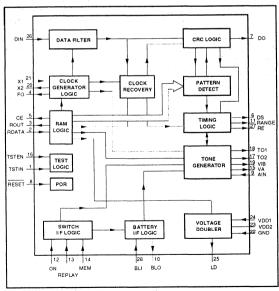

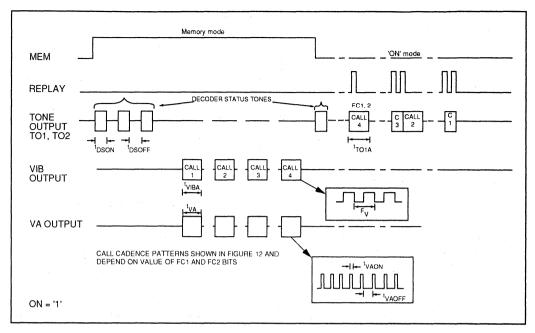

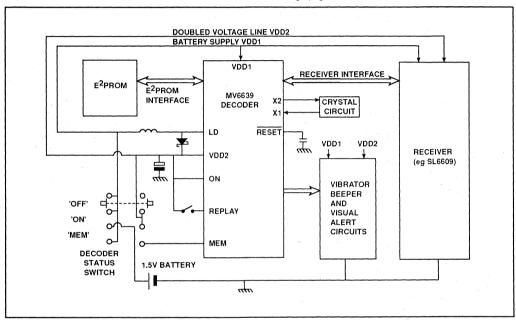

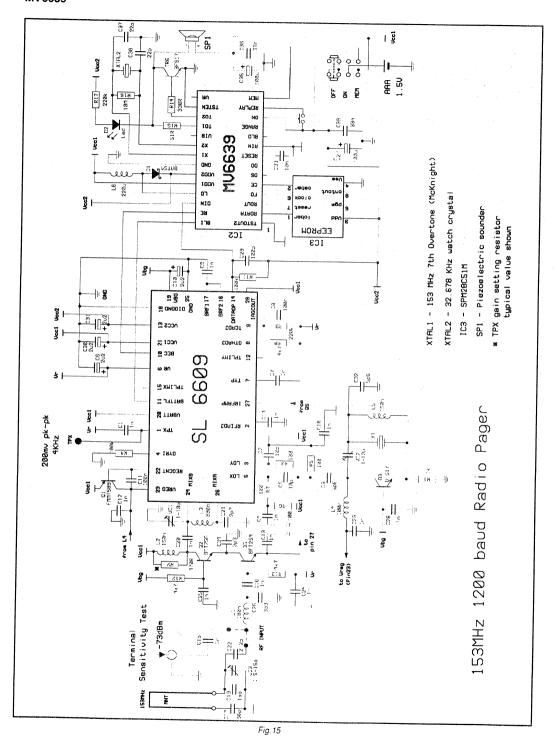

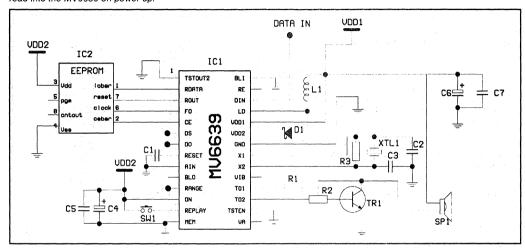

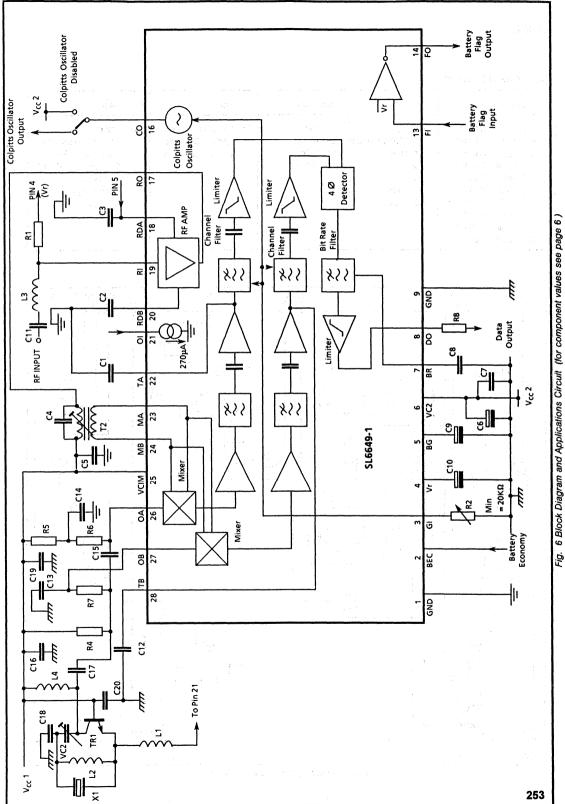

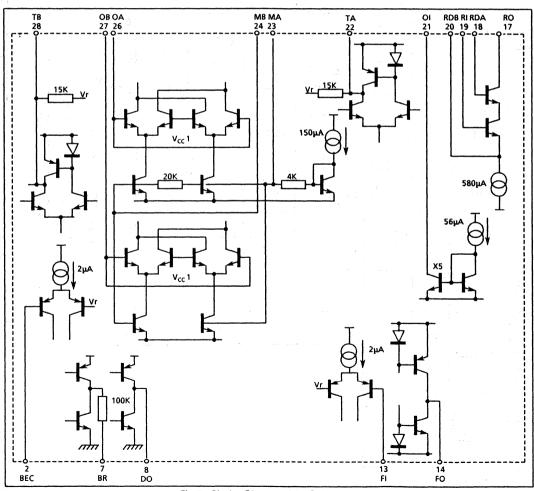

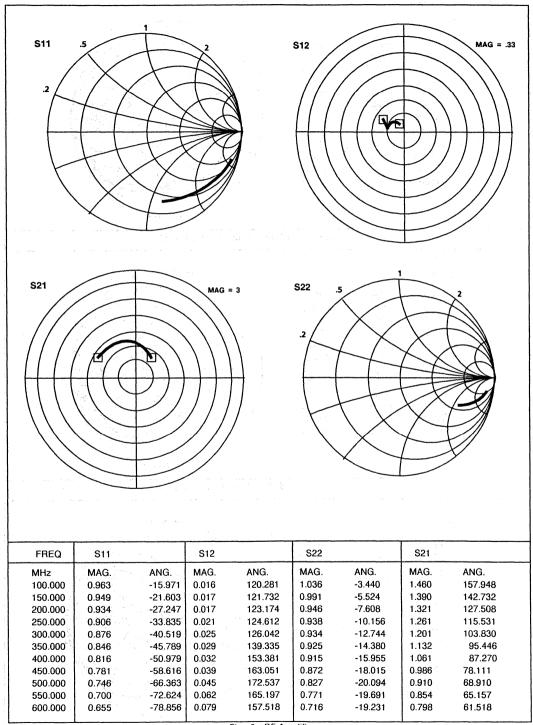

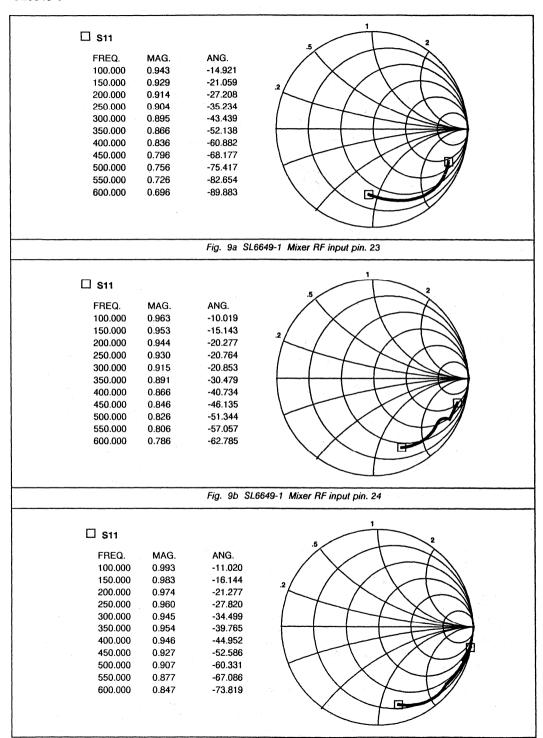

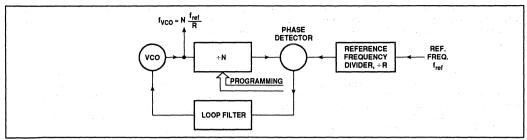

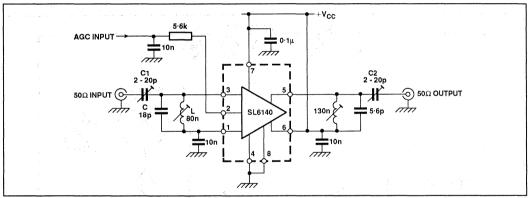

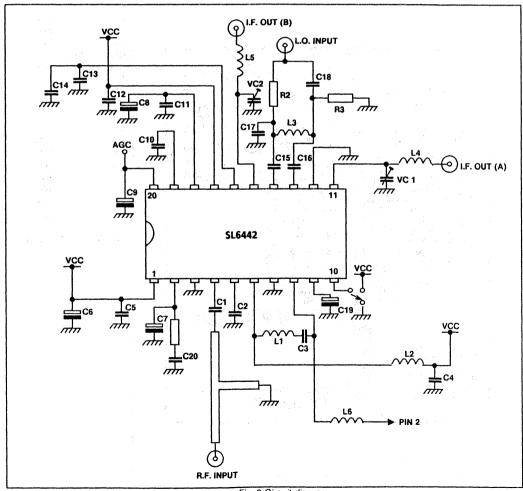

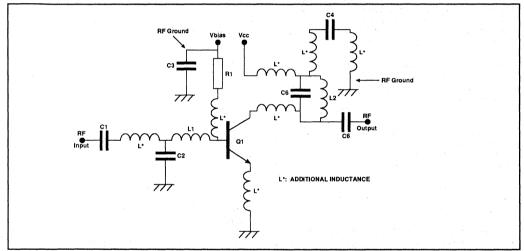

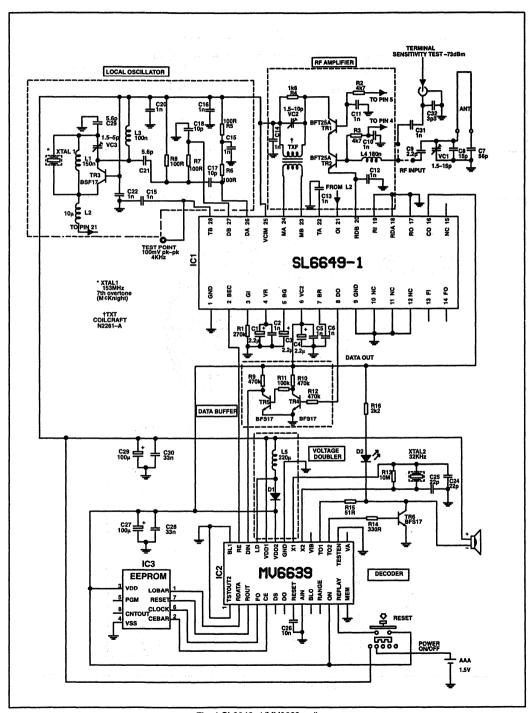

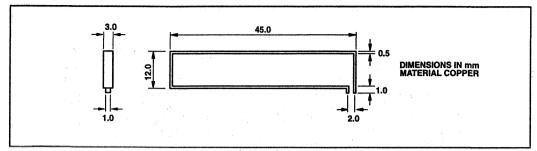

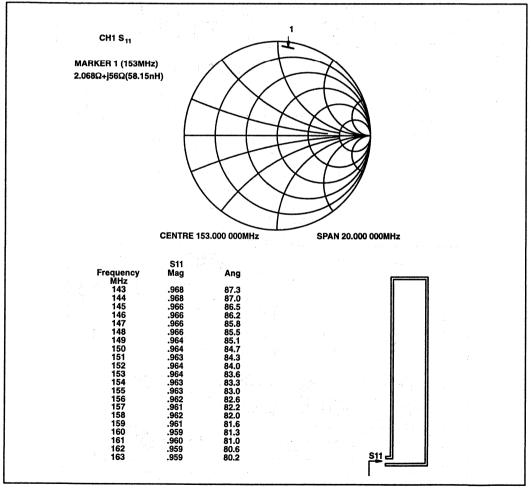

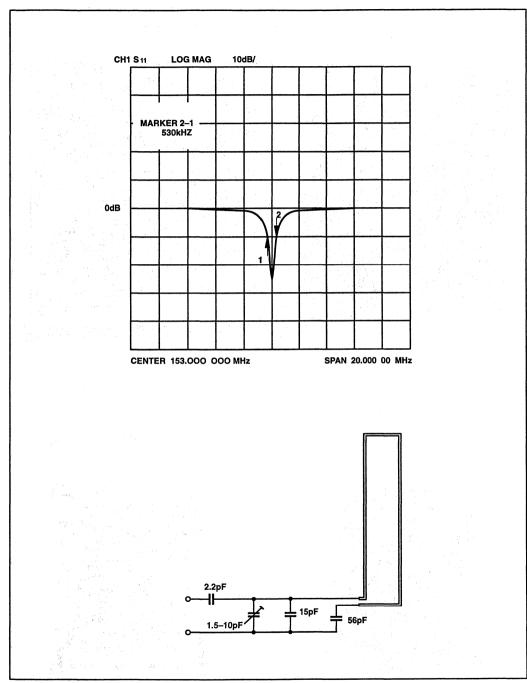

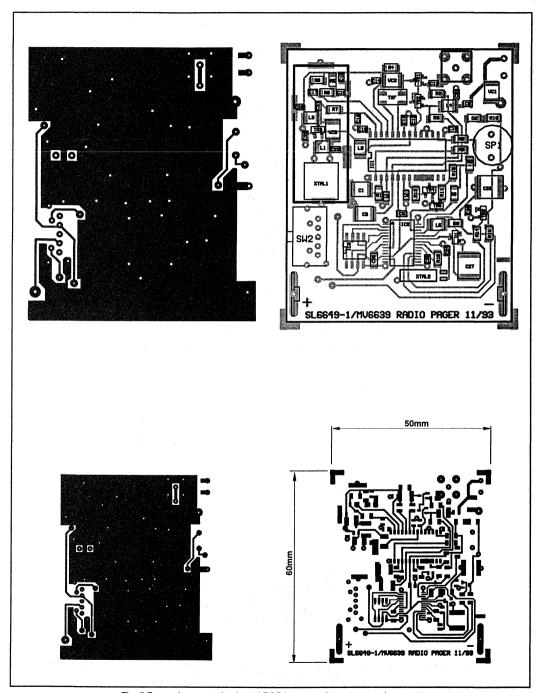

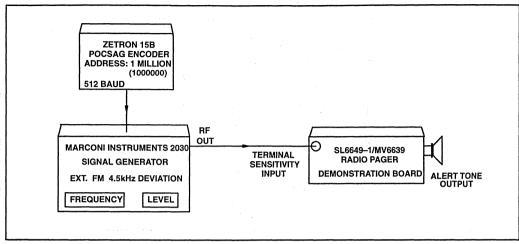

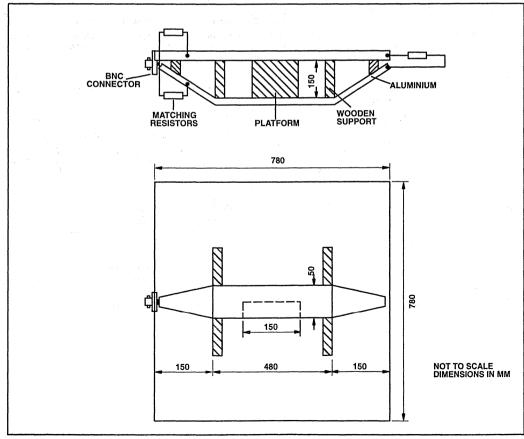

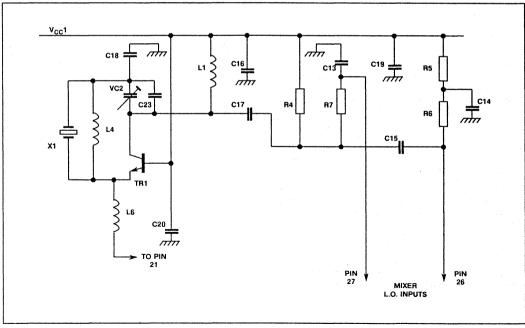

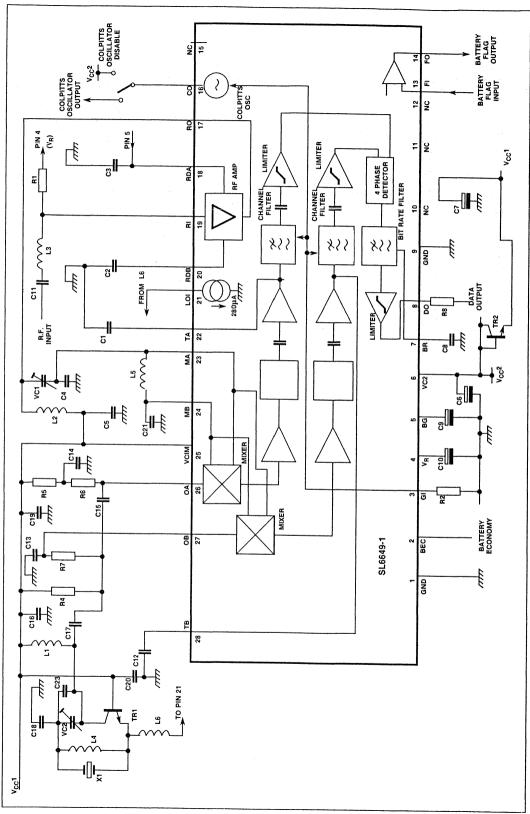

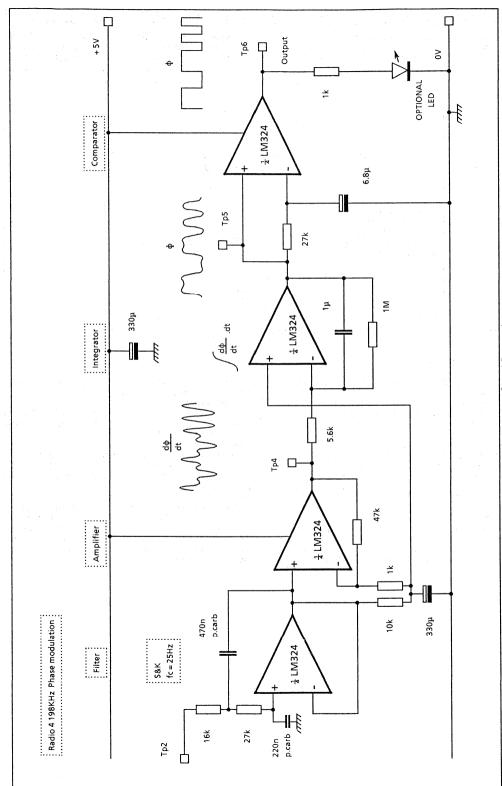

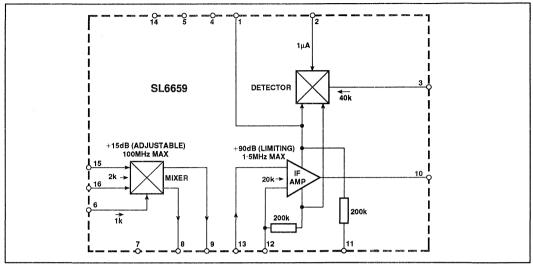

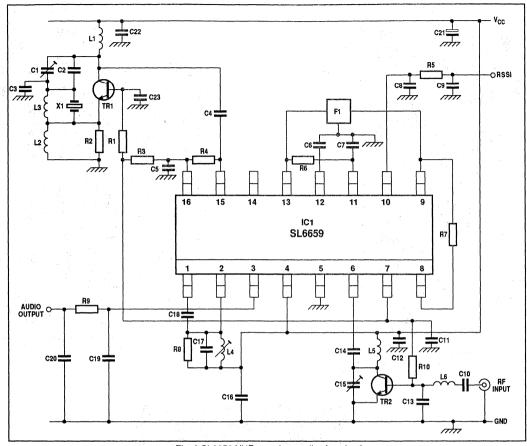

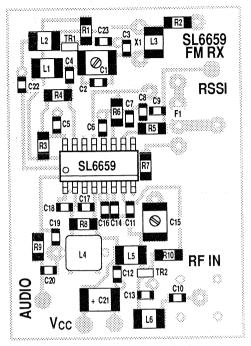

| Gain programming resistor, RB                                   | 5    |                |           | kΩ    |                                                       |  |